SPI means Serial Peripheral Interface.

The Serial Peripheral Interface Bus or SPI bus is a synchronous serial data link de facto standard, named by Motorola, that operates in full duplex mode. Devices communicate in master/slave mode where the master device initiates the data frame. Multiple slave devices are allowed with individual slave select (chip select) lines. Sometimes SPI is called a four-wire serial bus, contrasting with three-, two-, and one-wire serial buses. SPI is often referred to as SSI (Synchronous Serial Interface).

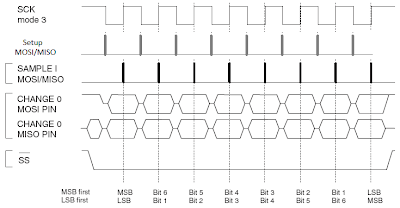

The SPI Mode 3 waveform is

We have seen the working of SPI and the SPI Master in the previous page. Now let us see about the SPI Slave.Click here to goto SPI MASTER Page.

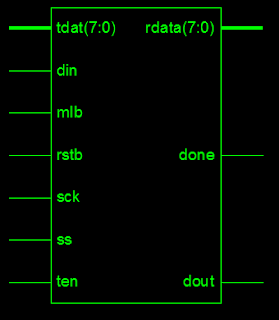

SPI SLAVE VERILOG MODULE:

The slave module is simple. It is just like a shift register with additional control signal SS_bar. The data is sampled in at positive edge of SCK and shifted out at negative edge of SCK. The data transmission of slave is active only when SS_bar input signal is low, otherwise it is disconnected from the bus & Sdout is tri-stated. Other control signals are similar to that of SPI Master Module.

SPI Slave Block Diagram is

The SPI Slave module verilog code is as follows:

//read from sdin

always @(posedge sck or negedge rstb)

begin

if (rstb==0)

begin rreg = 8'h00; rdata = 8'h00; done = 0; nb = 0; end //

else if (!ss) begin

if(mlb==0)

begin rreg ={sdin,rreg[7:1]}; end

else

begin rreg ={rreg[6:0],sdin}; end

nb=nb+1;

if(nb!=8) done=0;

else begin rdata=rreg; done=1; nb=0; end

end

end

//send to sdout

always @(negedge sck or negedge rstb)

begin

if (rstb==0)

begin treg = 8'hFF; end

else begin

if(!ss) begin

if(nb==0) treg=tdata;

else begin

if(mlb==0)

begin treg = {1'b1,treg[7:1]}; end

else

begin treg = {treg[6:0],1'b1}; end

end

end //!ss

end //rstb

end //always

//read from sdin

always @(posedge sck or negedge rstb)

begin

if (rstb==0)

begin rreg = 8'h00; rdata = 8'h00; done = 0; nb = 0; end //

else if (!ss) begin

if(mlb==0)

begin rreg ={sdin,rreg[7:1]}; end

else

begin rreg ={rreg[6:0],sdin}; end

nb=nb+1;

if(nb!=8) done=0;

else begin rdata=rreg; done=1; nb=0; end

end

end

//send to sdout

always @(negedge sck or negedge rstb)

begin

if (rstb==0)

begin treg = 8'hFF; end

else begin

if(!ss) begin

if(nb==0) treg=tdata;

else begin

if(mlb==0)

begin treg = {1'b1,treg[7:1]}; end

else

begin treg = {treg[6:0],1'b1}; end

end

end //!ss

end //rstb

end //always

Hey What s the significance of "tdat" in Slave module... i'm not getting... can you explain me abt tat plz....

ReplyDeleteVery nice tutorial, but I was wondering where is the link for spi slave, master and test-bench. The link provided is broken.

ReplyDeleteelazığ

ReplyDeletebilecik

kilis

sakarya

yozgat

JİEPS

https://titandijital.com.tr/

ReplyDeletediyarbakır parça eşya taşıma

nevşehir parça eşya taşıma

bolu parça eşya taşıma

batman parça eşya taşıma

VGSV2

kırşehir evden eve nakliyat

ReplyDeletegiresun evden eve nakliyat

tekirdağ evden eve nakliyat

ardahan evden eve nakliyat

izmir evden eve nakliyat

7KEXC

C20DD

ReplyDeleteTokat Şehir İçi Nakliyat

Afyon Evden Eve Nakliyat

Edirne Evden Eve Nakliyat

Gümüşhane Evden Eve Nakliyat

Sinop Parça Eşya Taşıma

Hakkari Şehirler Arası Nakliyat

Çorum Şehirler Arası Nakliyat

Elazığ Şehirler Arası Nakliyat

Sivas Şehir İçi Nakliyat

AF073

ReplyDeletebkex

kredi kartı ile kripto para alma

papaya

binance ne demek

okex

binance

telegram en iyi kripto grupları

bitexen

telegram türk kripto kanalları

79925

ReplyDeletekripto para haram mı

bybit

bitcoin nasıl oynanır

gate io

binance referans kodu

binance referans kod

bybit

kripto para nasıl alınır

kraken

C7F5E

ReplyDeleteGoogle SEO

fuar standı

Facebook Para Kazanma

Online Oyunlar

jeneratör fiyatları

Netflix Film Önerileri

Trendyol SEO

Google Yorum Satın Al

Tiktok SEO